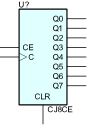

8-Bit Johnson Counter with Clock Enable and Asynchronous Clear

CJ8CE is a clearable Johnson/shift counter. The asynchronous clear (CLR) input, when High, overrides all other inputs and causes the data outputs (Q7 – Q0) to go to logic level zero, independent of clock (C) transitions. The counter increments (shifts Q0 to Q1, Q1 to Q2, and so forth) when the clock enable input (CE) is High during the Low-to-High clock transition. Clock transitions are ignored when CE is Low. The Q7 output is inverted and fed back to input Q0 to provide continuous counting operation.

Parameters

| Parameter | Description | Units | Default |

|---|---|---|---|

| DELAY | Propagation delay. | s | DGTDELAY |

| IN_MODE | Inputs mode. | IN | |

| OUT_MODE | Outputs mode. | OUT | |

| IOMODEL | The name of an I/O model, which describes the device’s loading and driving characteristics. | DGTDEFIOMODEL | |

| POWER_NODE | Digital power node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DPWR | |

| GROUND_NODE | Digital ground node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DGND |