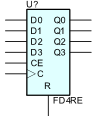

4-Bit Data Register with Clock Enable and Synchronous Reset

When the clock enable (CE) input is High, and the synchronous reset (R) input is Low, the data on the four data inputs (D3 – D0) of FD4RE is transferred to the corresponding data outputs (Q3 – Q0) during the Low-to-High clock (C) transition. When R is High, it overrides all other inputs and resets the data outputs (Q3 – Q0) Low on the Lowto- High clock transition. When CE is Low, clock transitions are ignored.

Parameters

| Parameter | Description | Units | Default |

|---|---|---|---|

| IC | Output initial state. | LOW | |

| CLKTPLH | Delay from clock to out high. | s | DGTDELAY |

| CLKTPHL | Delay from clock to out low. | s | DGTDELAY |

| CLRTPLH | Delay from reset to out high. | s | DGTDELAY |

| CLRTPHL | Delay from reset to out low. | s | DGTDELAY |

| IN_MODE | Inputs mode. | IN | |

| OUT_MODE | Outputs mode. | OUT | |

| IOMODEL | The name of an I/O model, which describes the device’s loading and driving characteristics. | DGTDEFIOMODEL | |

| POWER_NODE | Digital power node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DPWR | |

| GROUND_NODE | Digital ground node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DGND |