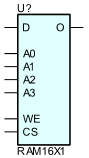

16-Deep by 1-Wide Static RAM

The digital RAM is an 1-wide, 16-deep random access memory element with

programmable select lines, tristated data_out lines, and a single write/read

line.

There is no reset line into the device. However, an initial

value for all bits may be specified by setting the ic parameter to either 0 or

1. In reading a word from the ram, the read_delay value is invoked, and output

will not appear until that delay has been satisfied. Separate rise and fall

delays are not supported for this device.

Note that UNKNOWN inputs on

the address lines are not allowed during a write. In the event that an address

line does indeed go unknown during a write, THE ENTIRE CONTENTS OF THE RAM WILL

BE SET TO UNKNOWN. This is in contrast to the data_in lines being set to unknown

during a write; in that case, only the selected word will be corrupted, and this

is corrected once the data lines settle back to a known value. Note that

protection is added to the write_en line such that extended UNKNOWN values on

that line are interpreted as ZERO values. This is the equivalent of a read

operation and will not corrupt the contents of the RAM. A similar mechanism

exists for the select lines. If they are unknown, then it is assumed that the

chip is not selected.

Parameters

| Parameter | Description | Units | Default |

|---|---|---|---|

| IC | Initial bit state (0, 1, 2). | 1 | |

| READ_DELAY | Read delay from address/select/write_en active. | s | DGTDELAY |

| IN_MODE | Inputs mode. | IN | |

| OUT_MODE | Outputs mode. | OUT | |

| IOMODEL | The name of an I/O model, which describes the device’s loading and driving characteristics. | DGTDEFIOMODEL | |

| POWER_NODE | Digital power node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DPWR | |

| GROUND_NODE | Digital ground node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DGND |