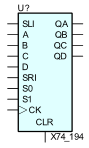

4-Bit Loadable Bidirectional Serial/Parallel-In Parallel-Out Shift Register

X74_194 is a 4-bit shift register with shift-right serial input (SRI), shift-left serial input (SLI), parallel inputs (D – A), parallel outputs (QD – QA), two control inputs (S1, S0), and active-Low asynchronous clear (CLR). The shift register performs the following functions.

- Clear. When CLR is Low, all other inputs are ignored and outputs QD – QA go to logic state zero during the Low-to-High clock transition.

- Load. When S1 and S0 are High, the data on inputs D – A is loaded into the corresponding output bits QD – QA during the Low-to-High clock transition.

- Shift Right. When S1 is Low and S0 is High, the data is shifted to the next-highest bit position (right) as new data is loaded into QA (SRI->QA, QA->QB, QB->QC, and so forth).

- Shift Left. When S1 is High and S0 is Low, the data is shifted to the next-lowest bit position (left) as new data is loaded into QD (SLI->QD, QD->QC, QC->QB, and so forth).

Registers can be cascaded by connecting the QD output of one stage to the SRI input of the next stage, the QA output of one stage to the SRI input of the next stage, and connecting clock, S1, S0, and CLR inputs in parallel.

The default initial state of all flip-flops is zero.

Parameters

| Parameter | Description | Units | Default |

|---|---|---|---|

| DELAY | Propagation delay. | s | DGTDELAY |

| IN_MODE | Inputs mode. | IN | |

| OUT_MODE | Outputs mode. | OUT | |

| IOMODEL | The name of an I/O model, which describes the device’s loading and driving characteristics. | DGTDEFIOMODEL | |

| POWER_NODE | Digital power node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DPWR | |

| GROUND_NODE | Digital ground node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DGND |