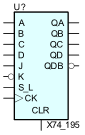

4-Bit Loadable Serial/Parallel-In Parallel-Out Shift Register

X74_195 is a 4-bit shift register with shift-right serial inputs (J and K), parallel inputs (D – A), parallel outputs (QD – QA) and QDB, shift/load control input (S_L), and active-Low asynchronous clear (CLR). Asynchronous CLR, when Low, overrides all other inputs and resets data outputs QD – QA Low and QDB High. When S_L is Low and CLR is High, data on the D – A inputs is loaded into the corresponding QD – QA bits of the register during the Low-to-High clock (C) transition. When S_L and CLR are High, the first bit of the register (QA) responds to the J and K inputs during the Low-to-High clock transition, as shown in the truth table. During subsequent Low-to- High clock transitions, with S_L and CLR High, the data is shifted to the next-highest bit position (shift right) as new data is loaded into QA (J, K->QA, QA->QB, QB->QC, and so forth).

Registers can be cascaded by connecting the QD and QDB outputs of one stage to the J and K inputs, respectively, of the next stage and connecting clock, S_L and CLR inputs in parallel.

The default initial state of all flip-flops is zero.

Parameters

| Parameter | Description | Units | Default |

|---|---|---|---|

| DELAY | Propagation delay. | s | DGTDELAY |

| IN_MODE | Inputs mode. | IN | |

| OUT_MODE | Outputs mode. | OUT | |

| IOMODEL | The name of an I/O model, which describes the device’s loading and driving characteristics. | DGTDEFIOMODEL | |

| POWER_NODE | Digital power node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DPWR | |

| GROUND_NODE | Digital ground node name. Is the node used by the interface subcircuits which connect analog nodes to digital nodes. | $G_DGND |